Zhengyu Chen, Jie Gu, Analysis and Design of Energy Efficient Time Domain Signal Processing, International Symposium on Low Power Electronic Design (ISLPED), 2016.

The paper is here

My first time ever heard about using time signal for ReRAM accelerator. Found this paper to learn some details.

Let’s see abstract first:

Time domain signal processing (TDSP) encodes information into time rather than voltage with higher efficiency than conventional digital design. This paper performs systematical analysis on the design principle and energy efficiency of TDSP. Variation impact, which poses significant challenges to TDSP, is evaluated and a variation driven design methodology is proposed to achieve an optimum tradeoff between energy efficiency and design robustness. Several novel circuit level design techniques such as dual encoding strategy and bit-scalable design are also proposed in this work to significantly improve the energy efficiency of TDSP. Design example on a critical building block of facial recognition application was used to demonstrate the potential of the technique. The result in a 45nm technology shows 3.3X energy-delay product reduction and 34% area saving can be achieved using TDSP compared with conventional digital.

1. Time signal processing

1.1 system

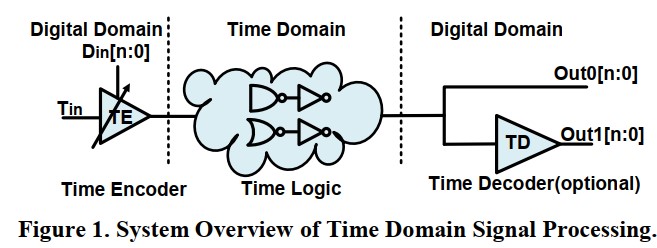

System is described in figure below. It’s composed of en/decoders and time domain logic.

1.2 Time Encoder

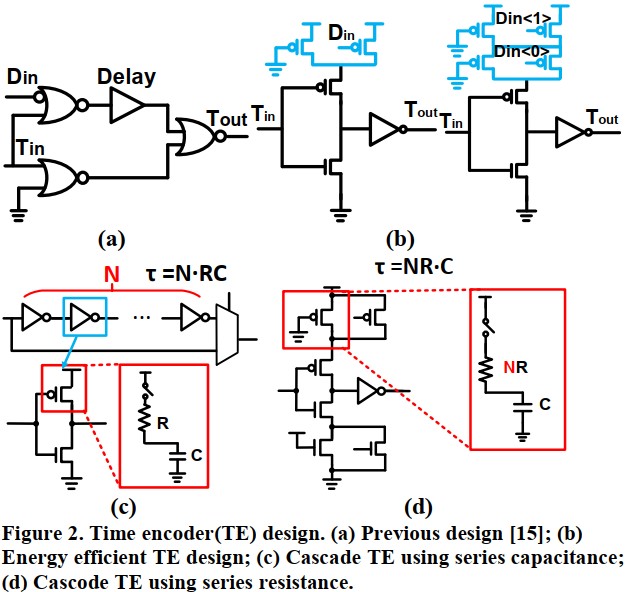

Time encoder is also called DTC (Digital-to-Time Converter). Figure below shows some impementation of DTCs.

Tech. (a) is proposed in This Paper. \(T_{in}\) is the time signal, such as Step Signal. \(D_{in}\) is the digital signal. By selecting different path with \(D_{in}\), delay of signal \(T_{out}\) is decided. The design suffer from energy problem because of (1) multiple gates (2) signal returning to original stage which cause \(2\times\) energy consumption.

Tech. (b) can encode multi-bit with a single inverter. (1) \(3\times\) energy saving compared to (a). (2) energy consumption is a constant even if embedding multi-bit.

Tech. (c)(d) are “Cascade TE”. To be further discuess in the next sections.

1.3 Dual-encoding Scheme

Compared to Tech. (a), which only encode information to only one kind of edge (raising or falling), this scheme means that encode information into both the two edges for energy saving. For more details, please refer to the paper.

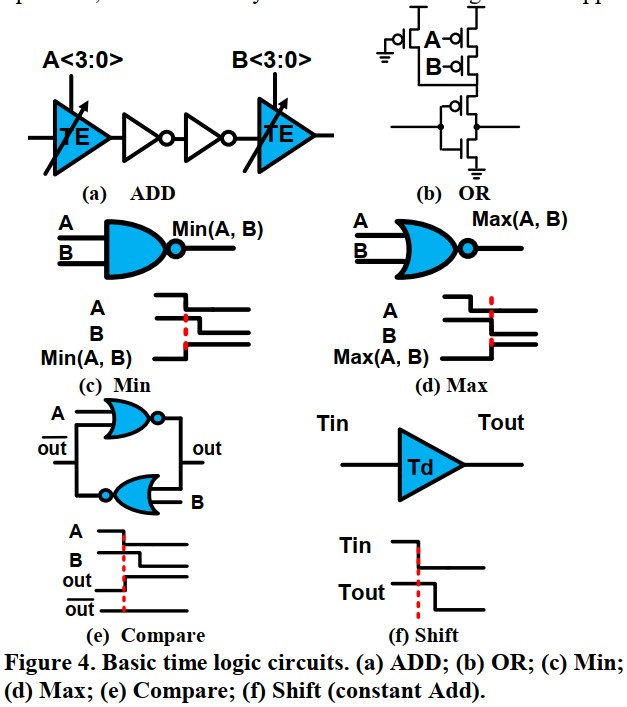

1.4 Time Logic Cell (TLC)

No more words, see the figure below.

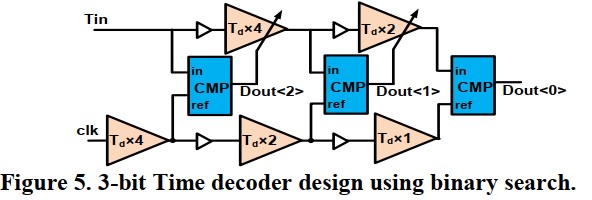

1.5 Time Decoder

A technology is described in figure blew. It is explicit and no more words.

2. Variation-Driven Design Methodology

2.1 Variation driven design

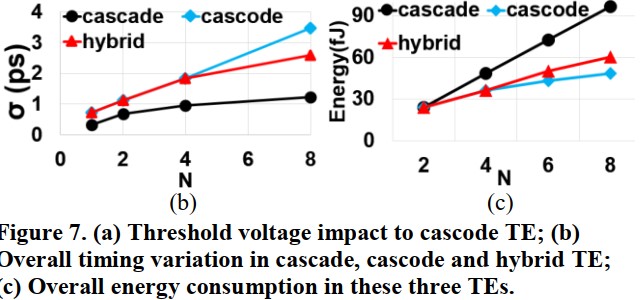

The auther introduces a energy-variation trade-off here. Consider the two kind of Tech. (c) (named cascade) and (d) (named cascode). As shown in figure below, cascade-type DTC has a larger energy but a smaller variation. Cascode-type DTC has an opposite characteristic. In order to trade off between energy and variation, a hybrid DTC is used.

Details of energy consumption and variation is described with the following equations:

\(\Delta T_{cascade\_TE}=\sqrt{2N}\sigma_1\)

\(\Delta T_{cascode\_TE}=\sqrt{\sum_{i=1}^{n}\left(A+N_i\sigma_2\right)^2}\)

\(\Delta T_{hybrid\_TE}=\sqrt{\sum_{i=1}^m\left(A+N_i\sigma_2\right)^2+\sum_{j=1}^{n-m}2^j\left(A+2^{m-1}\sigma_2\right)^2}\)

\(E_{cascade\_TE}=2N\cdot CV_{dd}^2\)

\(E_{cascode\_TE}=2nCV_{dd}^2\)

\(E_{hybrid\_TE}=\left(m+2^{n-m}\right)*2CV^2=\left(2m+2^{n-m+1}\right)CV^2\)

2.2 Simulated Variation Impact

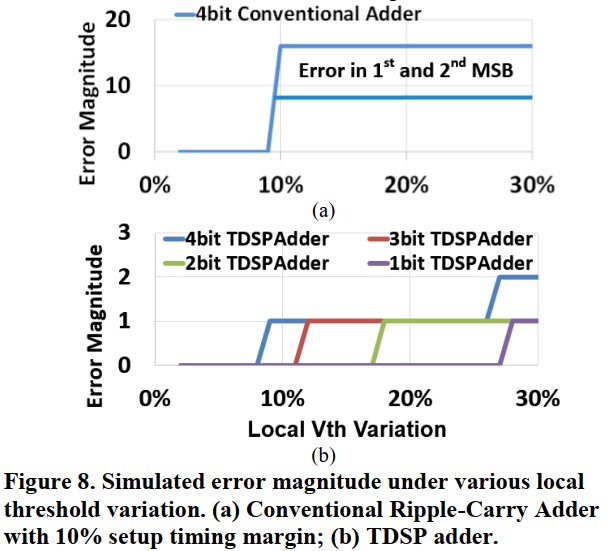

Simulated variation compared to conventional adder is shown in the figure below. It is amazing that time signal computing can achieve a such low variation.

3. Case Study

The following cases are studed in the origin paper:

- Big-scalable design

- Efficient MAX/MIN/CMP operation

- Parallel operation with short cirtical path

For more details, please refer to the origin paper.

4. Conclusion

Energy and area result is summrized in the following table:

| CPU | Conventional ASIC | TDSP | |

|---|---|---|---|

| Technology | 45nm, 1.1V | ||

| Energy (fJ) | 2304 | 323 | 224.4 |

| Area () | N/A | 115 | 75.6 |

| Delay (ns) | 3.2 | 0.98 | 0.43 |

Thoughts

First ReRAM-based DNN accelerator that uses time signal is Timely architecture. The author claims that TDC is much more energy efficient than ADC. This paper solve my confusion on how DTC and TDC works.

Actually, I think DAC and TDC can also be a conversion pair. With a capacitance used as integrator, along with a comparator, analog signal can be converted to time signal.

Moreover, the design in timely uses a circuit to store time signal, which is also what I am confused about.

文档信息

- 本文作者:Yilong Zhao

- 本文链接:https://xiaoke0515.github.io/2020/06/06/1_Time_signal/

- 版权声明:自由转载-非商用-非衍生-保持署名(创意共享3.0许可证)